sequential (105) No realistic serial circuit

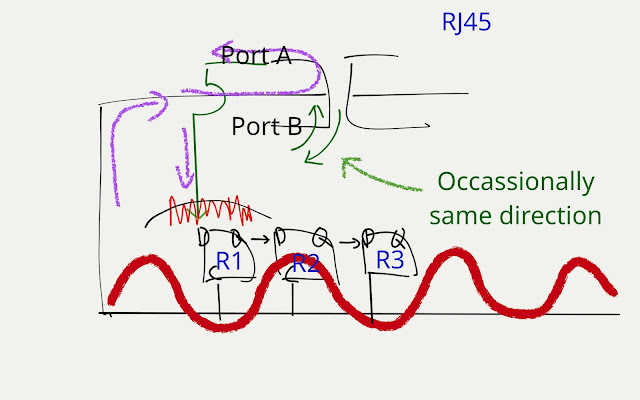

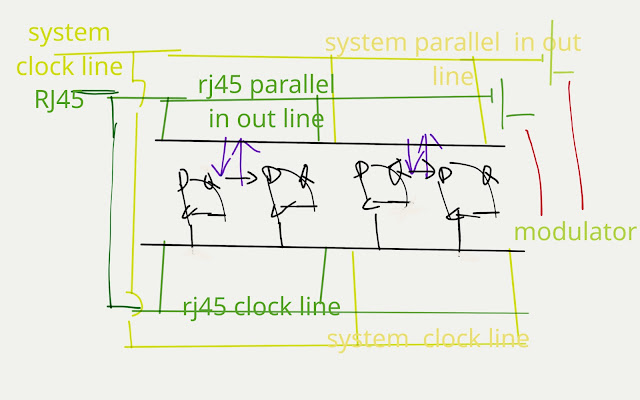

https://wodewangzhishime.blogspot.com/2024/02/blog-post.html . . Ref: https://wodewangzhishime.blogspot.com/2024/02/blog-post.html . . . . . John: The first and second picture is same. Me: OK. John: Look at the third picture. Me: OK. . John: Parallel in out line is a branch from the clock line of RJ 45. Me: Correct. ( Parallel in out line ) is a branch of the clock line of RJ45. John: Hacker hack the clock line of RJ 45, and , let the circuit beocme like this . while (RJ45 is running ) { Clock line of RJ45 = up cycle. Parallel in or out line = down cycle. }